## Introduction to Quantum Computing 量子計算入門 Rod Van Meter rdv@tera.ics.keio.ac.jp 寺岡研究室 September 28-30, 2004 @ Aizu U. with help from

#### Lecture Outline

伊藤公平 阿部英介 and Slides from T. Metodiev, T. Fujisawa

- Relationship of Architecture to Technology

- Criteria for Evaluating an Architecture

- example: layout

- An Advanced Architecture: Scalable Ion Trap

- Architecture in Action: Toward a Quantum Multicomputer

- Focus on mapping algorithm to architecture

#### Course Outline

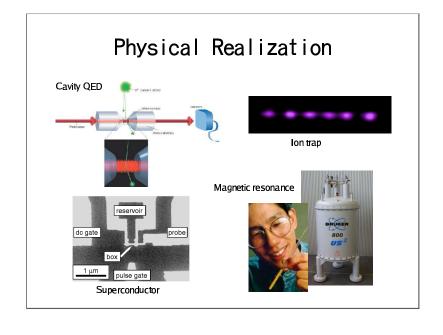

• Lecture 1: Introduction

• Lecture 2: Quantum Algorithms

• Lecture 3: Quantum Computational

Complexity Theory

• Lecture 4: Devices and Technologies

• Lecture 5: Quantum Computer Architecture

• Lecture 6: Quantum Networking

• Lecture 7: Wrapup

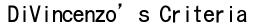

- Well defined extensible qubit array

- 2. Preparable in the "000..." state

- 3. Long decoherence time

- 4. Universal set of gate operations

- 5. Single quantum measurements

#### Architecture

- So far, we have described devices built on specific technologies

- System architecture is the Big Picture

- Technology influences architecture

- Architecture dictates behavior of algorithms

- Common assumption: simple line of qubits

#### **Problems**

- Coherence time

- nanoseconds for quantum dot, superconducting systems

- Gate time

- NMR-based systems slow (100s of Hz to low kHz)

- Gate quality

- generally, 60-70% accurate

- Interconnecting qubits

- Scaling number of qubits

- largest to date 7 qubits, most 1 or 2

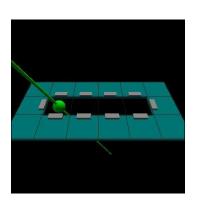

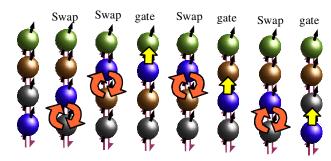

#### Scalable Ion Trap

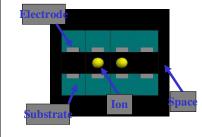

Qubits are represented in the electron spin of ions; the ions are physically moved around to bring them together to perform two-qubit gates. Gates are laser pulses that cause the qubits to rotate.

#### Quantum Computer Taxonomy

- flying or sedentary qubits?

- single v. ensemble

- concurrent gate support

- addressing

- natural gates ("instruction set")

- logical encoding

#### Technology is Not Architecture

The behavior of those two systems is completely different! We need a way to describe architecture, the way DiVincenzo describes technology...

#### Quantum Computer Taxonomy (2)

- internal topology

- quantum 1/0

- time: clock speed v. decoherence

- timing: jitter and skew control

- programmability

- operating temperature

- measurement time v. gate time

## Example: Layout (Internal Interconnect, Measurement)

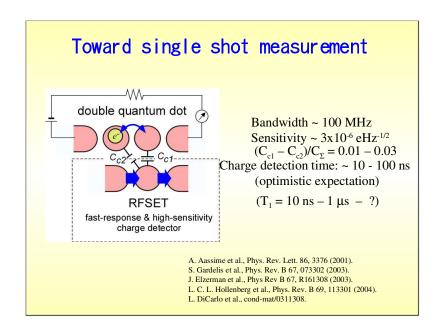

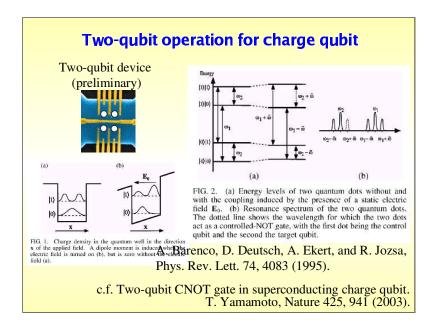

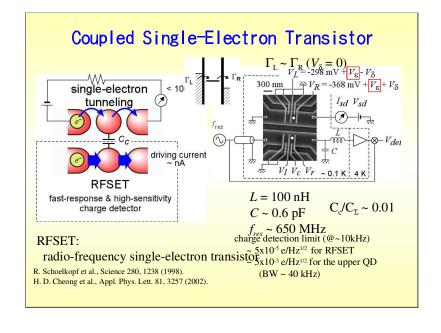

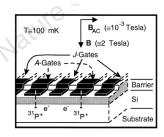

- Quantum dots as example

- Leads to dots require space

- Double-dot structure limits layout

- Measurement device requires space (fit with every qubit? probably not)

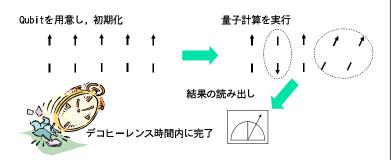

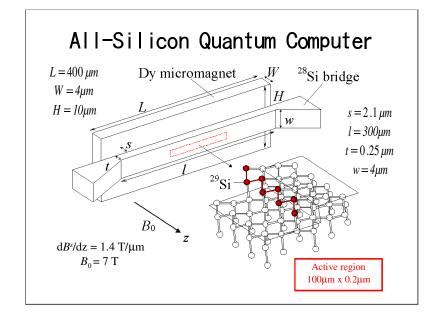

#### Kane Solid-State NMR

Qubits are stored in the spin of the nucleus of phosphorus atoms embedded in a zero-spin silicon substrate. Standard VLSI gates on top control electric field, allowing electrons to read nuclear state and transfer that state to another P atom.

Kane, Nature, 393(133), 1998

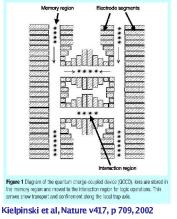

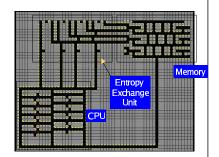

#### Advanced Architecture: Scalable Ion Trap

One of the few architectures that separates storage space from action space; that is, memory and CPU.

Main group is Wineland group at NIST (USA).

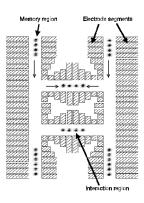

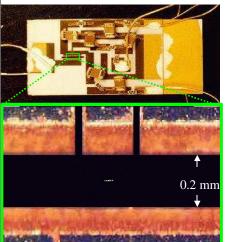

#### Kane/Oskin Lattice

Black dots are location of P atoms. Small rectangles are quantum-scale leads. Large squares are standard-size VLSI leads.

Fitting it all in is tough! This is the role of system architecture...

Oskin et al., ISCA, 2003

#### Trapped-Ion QIP

- Accomplishments:

- Deutsch-Josza algorithm

- Blatt group

- Guide, Nature 421, 48 (2003)

- 4 qubit entanglement

- Wineland group

Monroe, AIP Conf. Proc. 551 (2001)

- Ballistic transport

- Wineland group

- Rowe, Quantum Information and Computation 2, 257 (2002)

### Scalable Ion Trap QC: Architecture? • Scaling: mictrotraps

- Large-scale QC?

- Teleportation can be used for wiring & code conversion

- Gate errors ~ O(10<sup>-4</sup>) possible

#### Ion trap essentials:

#### RF Paul Trap Segments

- Substrates with attached electrodes for ion trapping and control

- Ions in linear chains

- Qubits are hyperfine states

- Oubits are coupled through collective vibrations

- Lasers implement logic gates and measurement

#### Gates and Measurement

- Quantum gates are laser pulses

- Two-qubit gates couple qubits via ion chain vibration

- Measurement uses a laser pulse and a detector

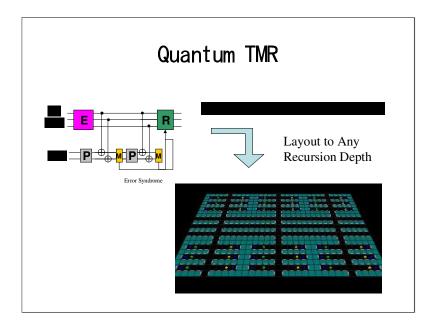

## Ion Trap Array Layout Quantum Circuit Layout and Physical Operations P = Prepare M = Measure0 = Initialize

#### General Quantum Architecture

- Processing Units and Memory

- Preparation and Initialization Units

- Communication Strategies

- Quantum Teleportation Channels

- Swap Channels

#### Architecture in Action: Designing a Quantum Multicomputer

- Focus: Designing a Quantum Multicomputer

- Down a Level: Architectural Algorithmic Analysis

- Down a Level: Fast Quantum Arithmetic

#### Goal: Design the Fastest, Most Scalable Quantum Computer Possible

Taking a page from the design of classical computers...

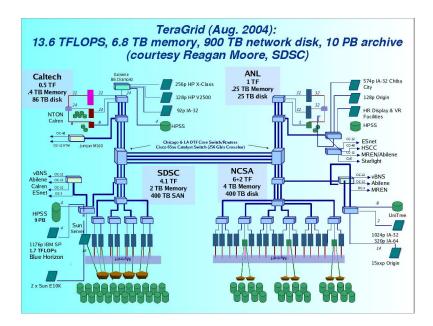

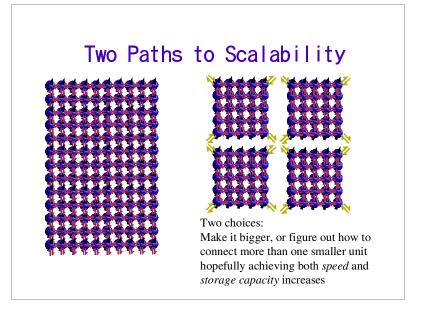

#### Two Paths to Scalability

Cray 1, 80MFLOPS, 8MB RAM, \$9M, 1976

Two choices:

Make it bigger, or figure out how to connect more than one smaller unit hopefully achieving both *speed* and *storage capacity* increases

Caltech Cosmic Cube, 64 processors (8086/7) 3MFLOPS, 8MB RAM, 1982 (prototype)

#### Two Paths to Scalability

Parallel/distributed computing has clearly "won". But the real lesson is not One Big v. Lots of Little; the lesson is that a group of computers can solve problems that an individual computer cannot. Even the biggest individual computer can be combined in a network to create a larger *system*.

## My Proposal: A Quantum Multicomputer

- Connect multiple, smaller "nodes" into larger system

- Independent control of each node

- Distributed memory

- Inter-node superposition required

#### Shor's Algorithm

- Uses Quantum Fourier Transform (QFT) in period-finding applications, including factoring large numbers

- (Actually, inverse of QFT, but reverse is simple in quantum)

- $-0(L^2)$

- Ignore for today (see my QIT10 paper)

- Also uses modular exponentiation

- O(L^3) with simple algorithm,

O(L^2 log L log log L) w/ more complex one

- Can be partially computed classically

#### **Problems**

- Constraint: Node capabilities are low

- Synchronization primitive

- How do we match time and control data structures in separate "nodes"?

- Reliable superposition transfer protocol

- Inter-node swaps initially probably high error rate

- Low level solution, or high level protocol?

- Algorithm distribution

- -e.g., Shor's algorithm

#### Algorithm Distribution

- What are the communication costs in the monolithic form of Shor's algorithm?

- How do they change for the distributed-memory form?

- Turns out algorithm definitions are excessively abstract (and slow) for estimating running time...

## Architectural Algorithm Analysis

- Modular exponentiation

- Vedral, Beckman, Gossett, Zalka...

- Many optimizations can be done

- faster modulo, parallel multiplication, better adders, hand optimization

- VERY dependent on architecture

- AC: abstract, w/ Toffoli

- TC: two-qubit gates only

- NTC: two-qubit, neighbors only

- Space and concurrency are critical!

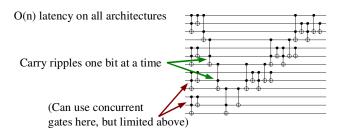

#### NTC: 1D Layout, Neighbors Only

Position first, then do action gates Only 1 new neighbor after each swap What's the performance penalty?

#### Carry-Ripple Adder

(Variants used in both major exponentiation algorithms, VBE (quant-ph/9511018) and BCDP (quant-ph/9602016).)

#### Carry-Ripple Adder

O(n) latency on all architectures

Carry ripples one bit at a time

(Can use concurrent gates in first time slot, then limited)

(Variants used in both major exponentiation algorithms, VBE (quant-ph/9511018) and BCDP (quant-ph/9602016).)

## O(log n) latency when long-distance gates are easy. O(n) when swap required (NTC architecture) -- with a big constant! Better use of concurrent gates (total still O(n) or larger). (Carry-save and carry-lookahead are other types that reach O(log n). See quant-ph/9808061, quant-ph/0406142.)

#### Conditional-Sum Adder (NTC)

O(log n) latency when long-distance gates are free. O(n) when swap required (NTC architecture) -- with a big constant!

Better use of concurrent gates (total still O(n) or larger).

(Carry-save and carry-lookahead are other types that reach O(log n). See quant-ph/9808061, quant-ph/0406142.)

#### Conditional-Sum Adder (AC)

O(log n) latency when long-distance gates are easy. O(n) when swap required (NTC architecture) -- with a big constant!

Better use of concurrent gates (total still O(n) or larger).

(Carry-save and carry-lookahead are other types that reach O(log n). See quant-ph/9808061, quant-ph/0406142.)

#### Latency for Mod Exp (128 bits)

|             | AC gates | perf | TC gates | perf | NTC gates | perf |

|-------------|----------|------|----------|------|-----------|------|

| VBE         | 1.25E+08 | 1    | 4.99E+08 | 1    | 8.32E+08  | 1    |

| BCDP        | 4.96E+07 | 2.5  | 1.32E+08 | 3.7  | 4.64E+08  | 1.8  |

| VBE (100n)  | 7.56E+06 | 16   | 3.03E+07 | 16   | 5.05E+07  | 17   |

| BCDP (100n) | 2.53E+06 | 49   | 6.71E+06 | 74   | 2.36E+07  | 35   |

| Α           | 2.65E+07 | 4.7  | 1.07E+08 | 4.7  | 1.77E+08  | 4.7  |

| В           | 3.71E+05 | 336  | 1.38E+06 | 360  | 1.71E+07  | 49   |

| С           | 1.22E+06 | 102  | 4.89E+06 | 102  | 8.11E+06  | 103  |

| D           | 2.19E+05 | 570  | N/A      |      | N/A       |      |

| E           | 1.71E+05 | 727  | N/A      |      | N/A       |      |

**B**, C, D, E, VBE(100n), BCDP(100n) use 100n storage; others use 5n-7n gates for AC are CCNOT, others are CNOT

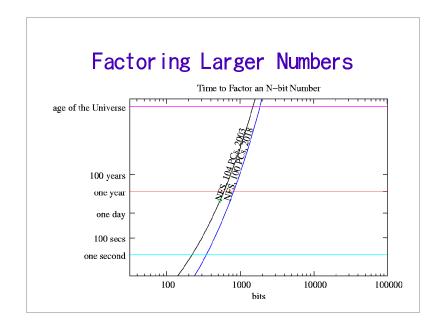

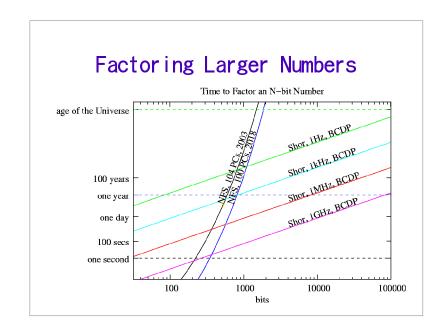

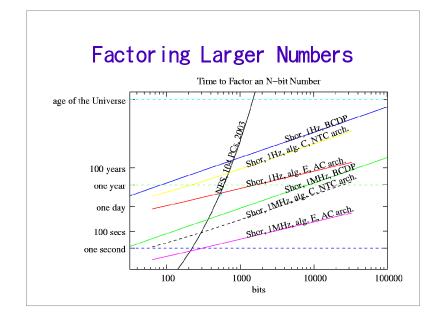

#### Factoring Larger Numbers

- 576 bits in a month current world record

- previous record, 512 bits using 104 PCs, one month

- 512 bits in one month requires

- using 5n space, no concurrency (original BCDP algorithm):

- AC arch: 2800 Hz logical CCNOT

- NTC arch: 78kHz logical 2-qubit gate

- using 100n space, high concurrency (rdv algorithms E, C):

- AC arch: 1.13 Hz logical CCNOT

- NTC arch: 130 Hz logical 2-qubit gate

#### Arithmetic Summary

- Basic exponentiation algorithms O(n^3)

- Constant factors are critical!!!!

- Architecture impacts constant factors and asymptotic performance

- Can reach O(log^3 n) w/ unlimited space on some architectures

- Other archs O(n<sup>2</sup> log n)

- Communications, concurrency important

- full paper at quant-ph/0408006

- JJAP letter in progress

- see also Fowler 0402196 & Devitt 0408081

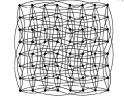

### Algorithms on Other Architectures

A lot is known about the computational complexity of circuits on arbitrary-interconnect machines; a little is known about circuit depth.

We and a few others (Fowler et al.) have investigated circuits on linear nearest neighbor (LNN or NTC) architectures.

Almost nothing is known about efficient circuits for 2D layout, lattices, scalable ion trap, etc.

# Open Question: 2D Layout Efficiency Does it give us an asymptotic change in O(.)? Single line layout Swap qubit values Neighbor only operations require swapping qubits 3xM layout roughly twice as efficient 3 new neighbors after each swap = 2/3 reduction in swaps

#### Conclusions

- Architecture impacts constant factors and asymptotic performance

- Key factors are concurrency, # of qubits, and interconnect topology

- Basic algorithms, including arithmetic, still need much work!

- Quantum multicomputer is ultimate goal

- Solve larger problems, maybe faster